IC封装及PCB设计的散热完整性

发布日期:2023-01-21

点击次数:1381

假如你现在正在构建一个专业设计的电路实验板,已经完成了layout前所有需要进行的仿真工作,并查看了厂商有关特定封装获得良好热设计的建议方法。你甚至仔细确认了写在纸上的初步热分析方程式,并确保其不超出IC结点温度,并有较为宽松的容限。但稍后,你打开电源,却发现IC摸起来非常热。对此,你感到非常不满,当然散热专家以及可靠性设计人员更加焦虑。现在,你该怎么办?

在谈到整体设计的可靠性时,通过让IC结点温度远离绝对最大值水平,在环境温度不断升高的条件下保持你的电路设计的完整性是一个重要的设计考虑因素。当你逐步接近具体电路设计中央芯片的最大功耗水平(Pd最大值)时更是如此。

进行散热完整性分析的第一步,是深入理解IC封装热指标的基础知识。

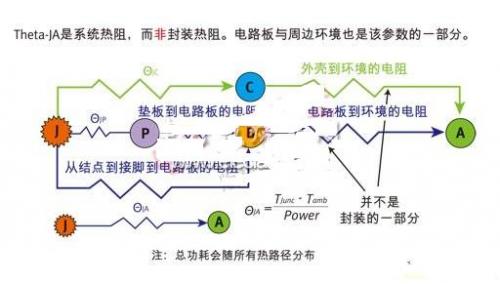

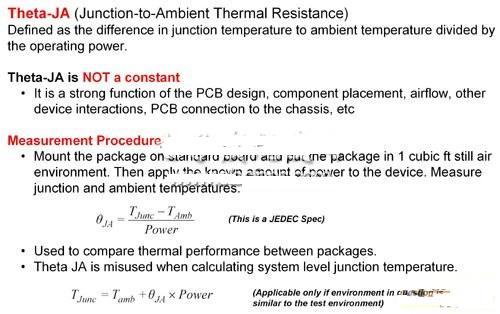

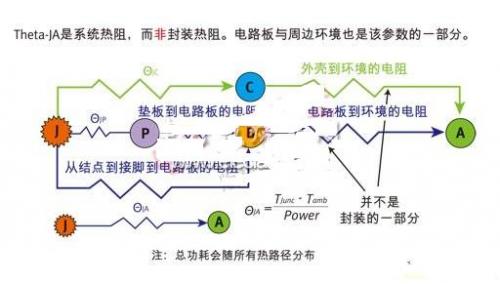

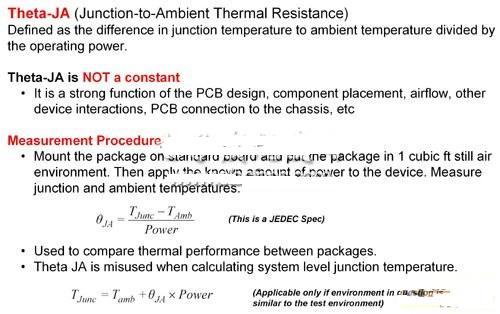

到目前为止,封装热性能最常见的度量标准是Theta JA,即从结点到环境所测得(或建模)的热阻(参见图1)。Theta JA值也是最需要解释的内容(参见图2)。能够极大影响Theta JA测量和计算的因素包括:

*贴装板:是/否?

*线迹:尺寸、成分、厚度和几何结构

*方向:水平还是垂直?

*环境:体积*靠近程度:有其他表面靠近被测器件吗?

图1电气网络Theta-JA分析

图2 Theta-JA解释

热阻(Theta JA)数据现在对使用新JEDEC标准的有引线表面贴装封装有效。实际数据产生于数个封装上,同时热模型在其余封装上运行。按照封装类型以及不同气流水平显示的Theta JA 值来对数据分组。

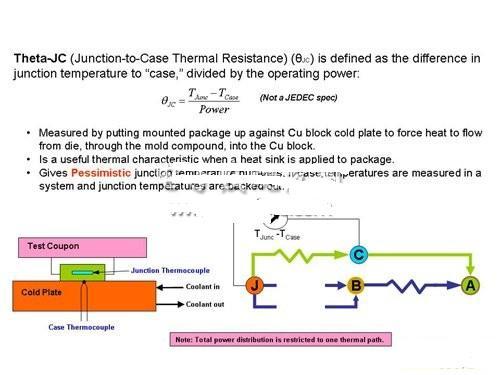

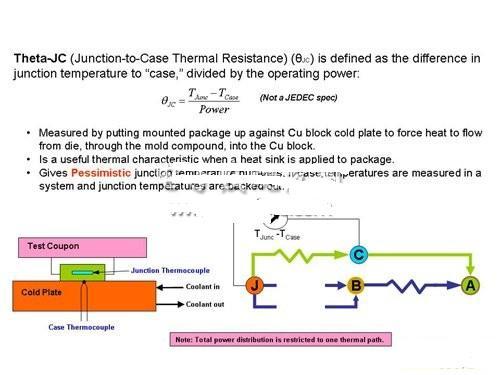

结点到环境数据是结点到外壳(Theta JC)的热阻数据(参见图3)。实际Theta JC数据会根据使用JEDEC印制电路板(PCB)测试的封装生成。